空間應(yīng)用中的 JESD204B 標(biāo)準(zhǔn)加速數(shù)據(jù)接口

出處:維庫(kù)電子市場(chǎng)網(wǎng) 發(fā)布于:2023-02-21 16:58:41

同時(shí),數(shù)據(jù)轉(zhuǎn)換器速度現(xiàn)已超過(guò) LVDS 接口速率的能力,商用數(shù)據(jù)轉(zhuǎn)換器行業(yè)已在很大程度上轉(zhuǎn)向聯(lián)合電子設(shè)備工程委員會(huì)JESD204B 串行接口標(biāo)準(zhǔn)。為了使空間有效載荷射頻 (RF) 收發(fā)器的帶寬提升到 LVDS 無(wú)法達(dá)到的水平,航天工業(yè)組件制造商將需要使用這種新的標(biāo)準(zhǔn)接口。

什么是 JESD204B?

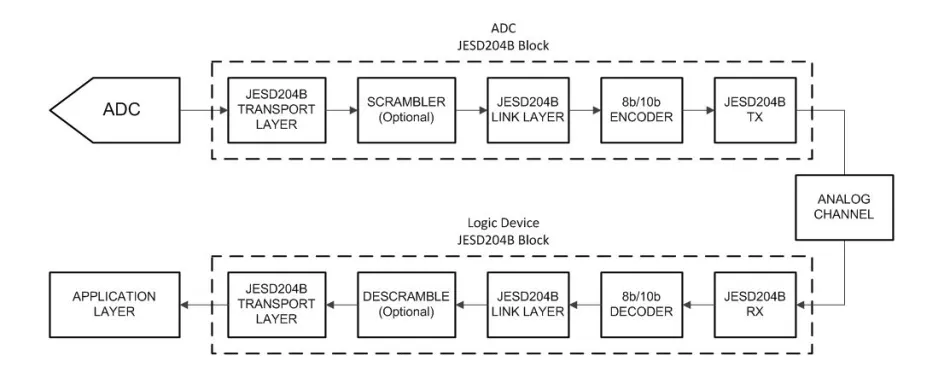

JESD204B 使用 8 位/10 位編碼數(shù)據(jù)接口通過(guò)差分通道將數(shù)據(jù)芯片串行化。這使得寬帶通信設(shè)計(jì)人員正在尋求超越 LVDS 的下一個(gè)信號(hào)帶寬水平取得突破,因?yàn)闀?shū)面 JESD204B 規(guī)范的上限是 12.5-Gbps 通道速率。設(shè)計(jì)人員可以使用此通道速率將多個(gè)轉(zhuǎn)換器聚合到一個(gè)通道中,或者可以采用多通道配置從一個(gè)數(shù)據(jù)轉(zhuǎn)換器傳輸大量數(shù)據(jù)到 FPGA 或從 FPGA 傳輸大量數(shù)據(jù)。

由于 JESD204B 不需要鏈路對(duì)之間的匹配走線長(zhǎng)度,因此設(shè)計(jì)人員可以?xún)?yōu)化電路板布線以節(jié)省電路板空間并避免 LVDS 通常需要的額外布線,以便將短的直線走線與長(zhǎng)的路徑相匹配。JESD204B 規(guī)范內(nèi)置了彈性緩沖以適應(yīng)走線長(zhǎng)度的變化。對(duì)于需要同步接收器的系統(tǒng),JESD204B 允許使用分布式低頻 SYSREF 信號(hào)的簡(jiǎn)單方法來(lái)實(shí)現(xiàn)多設(shè)備同步。

完善 JESD204B 生態(tài)系統(tǒng)

主要數(shù)據(jù)轉(zhuǎn)換器供應(yīng)商現(xiàn)在提供許多使用 JESD204B 標(biāo)準(zhǔn)的目錄(非航天級(jí))產(chǎn)品,目錄 FPGA 供應(yīng)商已經(jīng)生產(chǎn)了跟上(并且在大多數(shù)情況下超過(guò))當(dāng)前數(shù)據(jù)速度能力所必需的 JESD204B 知識(shí)產(chǎn)權(quán)轉(zhuǎn)換器。不幸的是,航天級(jí) FPGA 的 SerDes 輸入/輸出 (I/O) 速度受到限制,這減緩了航天應(yīng)用中從 LVDS 到 JESD204B 的過(guò)渡,因?yàn)檎w系統(tǒng)帶寬無(wú)法提高 LVDS 提供的帶寬。迄今為止,SerDes 的速度小于 5 Gbps,這在 Microchip RTG4 和 Xilinx Virtex-5QV 系列航天級(jí) FPGA 中都有。

如果業(yè)界曾嘗試在航天級(jí)組件中使用 LVDS 以超越 1.6 GSPS,則數(shù)據(jù)轉(zhuǎn)換器和 FPGA 之間將需要超過(guò) 100 對(duì)匹配長(zhǎng)度的差分連接。但是現(xiàn)在,有了 JESD204B,德州儀器ADC12DJ3200QML-SP等設(shè)備的數(shù)據(jù)量ADC 已經(jīng)能夠僅使用八個(gè)差分連接就達(dá)到了 6.4 GSPS。該器件通過(guò)以每條 12.8 Gbps 的速度運(yùn)行八個(gè) JESD204B SerDes 通道,實(shí)現(xiàn)了 6.4 GSPS 的 12 位數(shù)據(jù)輸出。現(xiàn)在可以想象繼續(xù)提高空間應(yīng)用的數(shù)據(jù)轉(zhuǎn)換器采樣率,方法是擴(kuò)展到更多差分連接、加速鏈路或兩者兼而有之。這將使信號(hào)帶寬和通過(guò) RF 鏈路傳輸?shù)叫l(wèi)星和從衛(wèi)星傳輸?shù)臄?shù)據(jù)速率大幅增加。

圖 1顯示了標(biāo)準(zhǔn)下的 SerDes 處理示例。模擬通道代表板上設(shè)備之間的高速數(shù)字?jǐn)?shù)據(jù)信號(hào)。此處將其稱(chēng)為模擬通道,因?yàn)?12.8-Gbps SerDes 鏈路在電路板設(shè)計(jì)和阻抗匹配中被視為模擬或 RF 信號(hào)。如果未對(duì)鏈路給予此關(guān)注,則接收端的眼圖將不會(huì)打開(kāi)和對(duì)齊以進(jìn)行正確捕獲。JESD204B 發(fā)送器是 ADC 序列化后的輸出數(shù)據(jù),JESD204B 接收器是需要反序列化的 FPGA(圖 1 中標(biāo)記為“邏輯設(shè)備”)的輸入。

然而,將空間應(yīng)用中的數(shù)據(jù)通信轉(zhuǎn)移到 JESD204B 不僅需要空間級(jí)數(shù)據(jù)轉(zhuǎn)換器,還需要空間級(jí) FPGA,它們可以協(xié)同工作以提供更高水平的信號(hào)帶寬。這些設(shè)備必須繼續(xù)提供太空任務(wù)所需的閉鎖和總電離劑量 (TID) 能力。

幸運(yùn)的是,這樣的設(shè)備很快就會(huì)面世。為了支持完整的 JESD204B 生態(tài)系統(tǒng),多家 FPGA 供應(yīng)商宣布他們將發(fā)布具有更快 SerDes 速度并支持 JESD204B 的航天級(jí) FPGA。例如,Xilinx 已宣布將在 XQRKU060 中將 Kintex UltraScale 類(lèi) FPGA 的一個(gè)版本過(guò)渡到太空級(jí),其中 32 個(gè) SerDes 收發(fā)器能夠?qū)崿F(xiàn) 12.5-Gbps 通道速率。圖 2是連接到 Alpha Data 板的 ADC12DJ3200QML-SP 板的圖片,Alpha Data 板包含用于 12.5-Gbps JESD204B 互操作性測(cè)試的 Xilinx XQRKU060。

JESD204B開(kāi)發(fā)板圖 2連接到Alpha Data 空間開(kāi)發(fā)套件(綠色)的ADC12DJ3200EVMCVAL (紅色)表明 JESD204B的空間級(jí)組件正可供設(shè)計(jì)人員使用。

其他供應(yīng)商也在效仿。NanoXplore 已宣布他們將提供空間級(jí) FPGA,在 NG-LARGE 中具有 6.25-Gbps SerDes,在 NG-ULTRA 中具有 12.5-Gbps SerDes。Microchip 宣布將在其太空級(jí)RT PolarFire FPGA變體中支持 24 個(gè) 10 Gbps SerDes 收發(fā)器。

如果沒(méi)有適當(dāng)?shù)臅r(shí)鐘解決方案將所有內(nèi)容同步連接在一起,F(xiàn)PGA-ADC 系統(tǒng)將無(wú)法工作。諸如航天級(jí)時(shí)鐘芯片 Texas Instruments LMX2615-SP 等設(shè)備現(xiàn)在可以提供高達(dá) 15 GHz 時(shí)鐘頻率的此功能。

JESD204B輻射特性

空間有效載荷設(shè)計(jì)人員在遇到重離子時(shí)需要了解使用 JESD204B 的設(shè)備的特性。盡管概率很低,但串行鏈路可能會(huì)被軌道上的重離子撞擊打斷。德州儀器 (TI) 在 2019 年核與空間輻射效應(yīng)會(huì)議上發(fā)布了 JESD204B 接口的單事件效應(yīng)表征。ADC12DJ3200QML-SP 的結(jié)果總結(jié)如下:

串行鏈路總是從重離子撞擊中自動(dòng)恢復(fù)。

串行鏈路的平均恢復(fù)時(shí)間為 1.3 ?s,壞情況下的測(cè)量值為 11 ?s。

但請(qǐng)記住,這些只是一個(gè)示例設(shè)備的結(jié)果。每個(gè)集成電路都會(huì)有不同的結(jié)果,因此需要在波束下進(jìn)行仔細(xì)的表征,以根據(jù)組件選擇、屏蔽環(huán)境和運(yùn)行軌道來(lái)確定總體誤碼率。如果重離子中斷鏈路,則需要具有正確錯(cuò)誤處理的符合 JESD204B 標(biāo)準(zhǔn)的接收器以實(shí)現(xiàn)快速恢復(fù)。

現(xiàn)在,支持航天級(jí)組件中 JESD204B 接口的數(shù)據(jù)轉(zhuǎn)換器、FPGA 和時(shí)鐘設(shè)備已經(jīng)面市,一個(gè)在太空應(yīng)用該標(biāo)準(zhǔn)的生態(tài)系統(tǒng)已經(jīng)建立。設(shè)計(jì)人員現(xiàn)在可以開(kāi)始處理寬帶衛(wèi)星通信和雷達(dá)有效載荷中的下一代系統(tǒng)帶寬。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://www.hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類(lèi)作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問(wèn)題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- USB-C接口全解析:協(xié)議兼容、快充原理與常見(jiàn)問(wèn)題排查2025/12/16 9:50:42

- 簡(jiǎn)述計(jì)算機(jī)總線的分類(lèi)2025/9/4 17:12:23

- 深度剖析三進(jìn)線兩母聯(lián)供電系統(tǒng)設(shè)計(jì)方案2025/9/3 10:37:39

- 匯流排是什么匯流排好還是線接好2025/8/28 17:13:00

- 安森美 USB - C 電池充電器解決方案2025/8/28 15:45:10

- 編碼器的工作原理及作用1

- 超強(qiáng)整理!PCB設(shè)計(jì)之電流與線寬的關(guān)系2

- 三星(SAMSUNG)貼片電容規(guī)格對(duì)照表3

- 電腦藍(lán)屏代碼大全4

- 國(guó)標(biāo)委發(fā)布《電動(dòng)汽車(chē)安全要求第3部分:人員觸電防護(hù)》第1號(hào)修改單5

- 通俗易懂談上拉電阻與下拉電阻6

- 繼電器的工作原理以及驅(qū)動(dòng)電路7

- 電容單位8

- 跟我學(xué)51單片機(jī)(三):?jiǎn)纹瑱C(jī)串口通信實(shí)例9

- 一種三極管開(kāi)關(guān)電路設(shè)計(jì)10

- MOSFET在汽車(chē)電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理

- 同步整流中MOSFET的應(yīng)用要點(diǎn)

- 輸出短路對(duì)電源芯片的影響

- 連接器壽命評(píng)估與可靠性設(shè)計(jì)

- PCB電源完整性(PI)設(shè)計(jì)核心實(shí)操規(guī)范

- 多層PCB疊層設(shè)計(jì)核心實(shí)操規(guī)范